File No. S360-21 Form C28-6811-1

# IBM System/360 Model 44

# **Programming System**

# Assembler Language

This publication contains specifications for the IBM System/360 Nodel 44 Programming System Assembler Language.

This assembler language is used to write programs for the Model 44. The IBM System/360 Model 44 Programming System Assembler program processes the language and provides auxiliary functions useful in the preparation and documentation of a program.

#### PREFACE

This publication is a reference manual for the programmer using the assembler language and its features.

This publication presents information common to all parts of the language, followed by specific information concerning the symbolic machine instruction codes and the assembler program functions provided for the programmer's use.

Appendixes A through F present such items as a summary chart for constants, instruction listings, character set representations, and other aids to programming. Appendix G is a features comparison chart of System/360 assemblers.

Knowledge of IBM System/360 machine operations, particularly storage addressing, data formats, and machine instruction formats and functions, is prerequisite to using this publication. It is assumed that the reader has experience with programming concepts and techniques or has completed basic courses of instruction in these areas.

The publications most closely supplemental to this one are:

IBM\_System/360: Principles of Operation, Form A22-6821

IBM System/360: System Summary, Form A22-6810

IBM System/360 Model 44: Functional Characteristics, Form A22-6875

IBM System/360 Model 44 Programming System: Concepts and Facilities, Form C28-6810

IBM System/360 Model 44 Programming System: Guide to System Use, Form C28-6812

Data Acquisition Special Features for IBM System/360 Model 44, Form A22-6900

#### Second Edition

This is a major revision of, and makes obsolete, C28-6811-0. Section 7, "Update Feature," has been substantially revised to include additional information and examples of update operations. Appendix G, "Features Comparison Checklists," has been rewritten to define more specifically the relationship between the IBM System/360 Model 44 Programming System Assembler Language and the other System/360 programming support system assembler languages. Because of a change in specifications, all references to the length attribute of a symbol have been deleted. Changes to the text other than these are indicated by a vertical line to the left of the change.

Specifications contained herein are subject to change from time to time. Any such change will be reported in subsequent revisions or Technical Newsletters.

Copies of this and other IBM publications can be obtained through IBM Branch Offices.

A form is provided at the back of this publication for reader's comments. If the form has been removed, comments may be addressed to IBM Corporation, Programming Publications, 1271 Avenue of the Americas, New York, N.Y., 10020.

n 1966 by International Business Machines Corporation

# CONTENTS

| SECTION 1: INTRODUCTION                              | ••  | 7            |

|------------------------------------------------------|-----|--------------|

| Compatibility                                        |     | 7            |

| The Assembler Language                               |     | 7            |

| Machine Operation Codes                              |     | 7            |

| Machine Operation Codes<br>Assembler Operation Codes | ••• | 78           |

| The Assembler Program                                |     | 7 N          |

| Basic Functions                                      |     | 8            |

| Programmer Aids                                      |     | 8            |

|                                                      |     |              |

| Programming System Relationships                     | ••• | 8 N          |

| SECTION 2: GENERAL INFORMATION                       | ••• | 9            |

| Assembler Language Coding Conventions                | ••• | 9            |

| Coding Form                                          | • • | 9            |

| Coding Form                                          |     | 10           |

| Summary of Statement Format                          |     | 11 E         |

| Identification-Sequence Field.                       | ••• | 11           |

| identification-sequence rieta.                       | ••  | 11           |

| Character Set                                        | ••• | <b>1</b> 1 s |

| Assembler Language Structure                         | • • | 11<br>s      |

| Terms And Expressions                                |     |              |

| Terms                                                | _   | 12           |

|                                                      | ••• | 12 I         |

| Symbols.                                             | ••• | 12 1         |

| Self-Defining Terms                                  |     |              |

| Location Counter Reference                           |     | 14           |

| Literals                                             |     |              |

|                                                      |     |              |

| EXPRESSIONS                                          | ••• | 10           |

| Evaluation of Expressions                            |     | 16           |

| Absolute and Relocatable                             |     |              |

| Expressions                                          |     | 17           |

|                                                      |     |              |

| SECTION 3: ADDRESSING PROGRAM                        |     |              |

| SECTIONING AND LINKING                               |     | 19           |

|                                                      |     |              |

| Addressing                                           |     | 19 I         |

| Addresses Explicit and Implied                       |     | 10           |

| Radiesses Expricit and impried                       | • • | 10           |

| Base Register Instructions                           | ••• | 19           |

| USING Use Base Address                               |     |              |

| Register                                             | • • | 19           |

| DROP Drop Base Register                              |     | 20           |

| Programming with the Using                           |     | . F          |

| Instruction.                                         |     | 20           |

|                                                      | ••• | 20           |

| Relative Addressing                                  | ••• | 21           |

|                                                      |     | 04           |

| Program Sectioning and Linking                       | • • | 21           |

| Control Sections                                     | • • | 22           |

| Control Section Location                             |     |              |

| Assignment.                                          |     | 22           |

|                                                      | ••• | 22           |

| START Start Assembly                                 | ••  |              |

| CSECT Identify Control                               |     | 5            |

| Section                                              | ••• | 23           |

| Unnamed Control Section                              |     | 23           |

| DSECT Identify Dummy Section                         |     | 23 V         |

| COM Define Common Control                            | - • |              |

|                                                      |     | 25 2         |

| Section.                                             | ••• | 25 S         |

| Symbolic Linkages                                    | ••• | 25           |

|                                                      |     |              |

| ENTRY Identify Entry-Point                                   |     |          |

|--------------------------------------------------------------|-----|----------|

|                                                              |     | 26       |

| Symbol                                                       | • • | 26       |

| Addressing External Control                                  |     |          |

|                                                              |     | 26       |

|                                                              |     |          |

| SECTION 4: MACHINE INSTRUCTIONS                              | ••• | 28       |

| Nachina Instantion Chatemants                                |     | 20       |

| Machine Instruction Statements<br>Instruction Alignment and  | ••• | 28       |

| Checking.                                                    |     | 28       |

| Operand Fields and Subfields.                                | ••  | 28       |

| operand ricids and bubileras.                                | ••• | 20       |

| Machine-Instruction Mnemonic Codes .                         |     | 29       |

|                                                              |     | 30       |

| RR Format.                                                   |     | 30       |

|                                                              |     | 30       |

| RX Format                                                    |     | 30       |

| SI Format                                                    | • • | 30       |

|                                                              |     | • •      |

| Extended Mnemonic Codes                                      | ••  | 30       |

| SECTION 5. ASSEMBLER INSTRUCTION                             |     |          |

| STATEMENTS                                                   |     | 32       |

|                                                              | ••  | 52       |

| Symbol Definition Instruction                                |     | 32       |

| EQU EQUATE SYMBOL                                            |     | 32       |

|                                                              |     |          |

| Data definition Instructions                                 | •   | 33       |

| DC Define Constant                                           | •   | 33       |

| Operand Subfield 1: Duplication                              |     |          |

| Factor                                                       | •   | 34       |

| Operand Subfield 2: Type                                     | •   | 34       |

| Operand Subfield 3: Length                                   | •   | 34       |

| Operand Subfield 4: Constant                                 | •   | 35<br>38 |

| DS Define Storage                                            | ••  | 38       |

|                                                              |     | 39       |

| CCW Define Channel Command Word.                             | • • | 40       |

| cew berine chamier command word                              | ••  | 40       |

| Listing Control Instructions                                 |     | 40       |

| TITLE Identify Assembly Output .                             |     | 40       |

| EJECT Start New Page                                         | •   | 41       |

| SPACE Space Listing                                          | •   | 41       |

| PRINT Print Optional Data                                    | •   | 42       |

|                                                              |     |          |

| Program Control Instructions                                 | •   | 42       |

| ICTL Input Format Control                                    | •   | 43       |

| REPRO Reproduce Following Card .<br>ORG Set Location Counter | •   | 43       |

| LTORG Begin Literal Pool                                     | •   | 43       |

| Duplicate Literals                                           |     | 44       |

| CNOP Conditional No Operation.                               | •   |          |

| END End Assembly                                             |     |          |

|                                                              | -   |          |

| SECTION 6: CONDITIONAL ASSEMBLY                              |     |          |

| INSTRUCTIONS                                                 | •   | 46       |

|                                                              |     |          |

| Variable Symbols                                             | •   | 46       |

| SETA Set Arithmetic                                          |     | 11 6     |

| SEIN Set ALTCHMECTC                                          | •   | 40       |

|                                                              |     |          |

| Evaluation of Arithmetic<br>Expressions 46                          | SKP1<br>CPY1                         |

|---------------------------------------------------------------------|--------------------------------------|

| Logical Expressions 47                                              | R EWN<br>ENDU                        |

| Sequence Symbols 47                                                 | Sequence (                           |

| AIF Conditional Branch 48                                           | Examples o                           |

| AGO Unconditional Branch 48                                         | APPENDIX A                           |

| ANOP Assembly No Operation 48                                       | APPENDIX E                           |

| Using Conditional Assembly<br>Instructions 48                       | APPENDIX C                           |

| SECTION 7: UPDATE FEATURE 50                                        | APPENDIX I<br>OPERATION              |

| Input/Output Considerations 50                                      | APPENDIX                             |

| Update Operation                                                    | APPENDIX F                           |

| Update Instructions 51<br>NUM Instruction 51<br>OMIT Instruction 52 | APPENDIX C<br>LANGUAGES<br>CHECKLIST |

| • | •           | • | 46<br>47       | SKPTO Instruction.52CPYTO Instruction.53REWND Instruction.53ENDUP Instruction.53 |

|---|-------------|---|----------------|----------------------------------------------------------------------------------|

| • | •           | • | 47             | Sequence Checking 54                                                             |

| • | •           | • | 48             | Examples of Update Operation 54                                                  |

| • | •           | • | 48             | APPENDIX A: CHARACTER CODES 57                                                   |

| • | •           | • | 48             | APPENDIX B: HEXADECIMAL-DECIMAL NUMBER<br>CONVERSION TABLE 62                    |

| • | •           | • | 48             | APPENDIX C: MACHINE-INSTRUCTION FORMAT . 67                                      |

| • | •           | - | 50             | APPENDIX D: MACHINE-INSTRUCTION<br>OPERATION CODES                               |

| • | •           | - | 50             | APPENDIX E: ASSEMBLER INSTRUCTIONS 71                                            |

| • | •<br>•      | • | 50<br>50<br>51 | APPENDIX F: SUMMARY OF CONSTANTS 72                                              |

| • | •<br>•<br>• | • | 51<br>51<br>52 | APPENDIX G: ASSEMBLER<br>LANGUAGESFEATURES COMPARISON<br>CHECKLISTS              |

|   |             |   |                |                                                                                  |

FIGURES

TABLES

Computer programs may be expressed in machine language, i.e., language interpreted directly by the computer, or in a symbolic language, which is much more meaningful to the programmer. The symbolic language, however, must be translated into machine language before the computer can execute the program. This function is accomplished by a processing program.

Of the various symbolic programming languages, assembler languages are closest to machine language in form and content. The assembler language discussed in this publication is a symbolic programming language for the IBM System/360 Model 44. It enables the programmer to use IBM System/360 machine functions as though he were coding in System/360 Model 44 machine language.

The assembler program that processes the language translates symbolic instructions into machine-language instructions, assigns storage locations, and performs auxiliary functions necessary to produce an executable machine-language program.

# COMPATIBILITY

The IBM System/360 Model 44 Programming System Assembler Language is a selected subset of the language available in the IBM System/360 programming support systems designed for the Models 30, 40, 50, 65, and 75 -- specifically:

- System/360 Operating System (OS/360)

- System/360 Disk Operating System (DOS/360)

- System/360 Tape Operating System (TOS/360)

Thus, source programs written in the Model 44 assembler language can be assembled by the appropriate assembler, OS/360, DOS/360, or TOS/360, provided that (1) any source statements involving subroutine linkages or supervisory functions are modified to the format specified for the applicable system, (2) there are no statements using instructions peculiar to the Model 44 or the Model 44 assembler program, and (3) all SETA variable symbols are defined using the LCLA or GBLA statements as specified in the appropriate language. Appendix G describes more specifically the relationship between the Model 44 Programming System Assembler Language and the other System/360 programming support system assembler languages.

# THE ASSEMBLER LANGUAGE

The basis of the assembler language is a collection of mnemonic symbols that represent:

- System/360 machine-language operation codes.

- Operations (auxiliary functions) to be performed by the assembler program.

The language is augmented by other symbols, supplied by the programmer, and used to represent storage addresses or data. Symbols are easier to remember and to code than are their machine-language equivalents. Use of symbols greatly reduces programming effort and error.

# Machine Operation Codes

The assembler language provides mnemonic machine-instruction operation codes for all machine instructions that can be processed by the Model 44 source programs and extended mnemonic operation codes for the conditional branch instruction. Appendix D lists the acceptable machine operation codes for Model 44 source programs.

## Assembler Operation Codes

The assembler language also contains mnemonic assembler-instruction operation codes, used to specify auxiliary functions to be performed by the assembler. These are instructions to the assembler program itself and, with a few exceptions, do not result in the generation of machinelanguage code by the assembler program.

## THE ASSEMBLER PROGRAM

The assembler program, also referred to as the "assembler," processes the source statements written in the assembler language.

# Basic Functions

Processing a source program involves the translation of source statements into machine language, the assignment of storage locations to instructions and other elements of the program, and the performance of the auxiliary assembler functions designated by the programmer. The output of the assembler program is the relocatable module, a machine-language translation of the source program. The assembler furnishes a printed listing of the source state-ments and object program statements and additional information useful to the programmer in analyzing his program, such as error indications. The object program is in the format required by the linkage editor component of the System/360 Model 44 Programming System.

# PROGRAMMER AIDS

The assembler provides auxiliary functions that assist the programmer in checking and documenting programs, in controlling address assignments, in segmenting a program, in data and symbol definition, and in controlling the assembler itself. Mnemonic operation codes for these functions are provided in the language.

Variety in Data Representation: Decimal, hexadecimal, or character representation of machine-language binary values may be employed by the programmer in writing source statements. The programmer selects the representation best suited to his purpose.

Base Register Address Calculation: As discussed in the publication IBM System/360: <u>Principles of Operation</u>, Form A22-6821, the System/360 addressing scheme requires the designation of a base register (containing a base address value) and a displacement value in specifying a storage location. The assembler assumes the clerical burden of calculating storage addresses in these terms for the symbolic addresses used by the programmer. The programmer retains control of base register usage and the values entered there.

<u>Relocatability:</u> The object programs produced by the assembler are in a format enabling relocation from the originally assigned storage area to any other suitable area. <u>Sectioning and Linking:</u> The assembler language and program provide facilities for partitioning an assembly into one or more parts called control sections. Control sections may be added or deleted when linkage editing the object program. Because control sections do not have to be loaded contiguously in storage, a sectioned program may be loaded and executed even though a continuous block of storage, large enough to accommodate the entire program, may not be available.

The assembler allows symbols to be defined in one assembly and referred to in another, thus effecting a link between separately assembled programs. This permits reference to data and transfer of control between programs. A detailed discussion of program sectioning and linking is contained in Section 3.

<u>Program Listings:</u> A listing of the source program statements and the resulting object program statements may be produced by the assembler for each source program it assembles. The programmer can control the form and content of the listing to some degree.

An alphabetical listing of all the symbols used in the program, together with cross references to the statements that use each symbol, can also be produced.

Error Indications: As a source program is assembled, it is analyzed for actual or potential errors in the use of the assembler language. Detected errors are indicated in the program listing, as described in the publication IBM System/360 Model 44 Programming System: Guide to System Use, Form C28-6812.

# PROGRAMMING SYSTEM RELATIONSHIPS

The assembler is a component of the IBM System/360 Model 44 Programming System and, as such, functions under control of the programming system. The programming system provides the assembler with input/output and other services needed in assembling a source program. In a like manner, the object program produced by the assembler will normally operate under control of the programming system and depend on it for input/output and other services. In writing the source program, the programmer uses the Supervisor Call (SVC) instruction to invoke the facilities of the programming system supervisor. The programming system supervisor is discussed in the publication IBM System/360 Model 44 Programming System: Concepts and Facilities, Form C28-6810. This section presents information about assembler language coding conventions, assembler source statement structure, and addressing.

### ASSEMBLER LANGUAGE CODING CONVENTIONS

This subsection discusses the general coding conventions associated with use of the assembler language.

## Coding Form

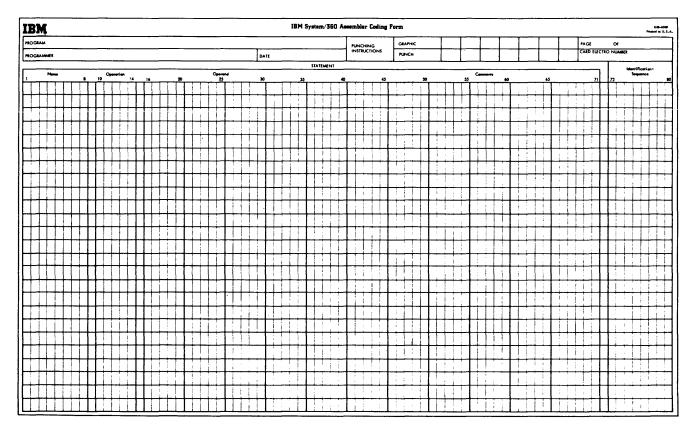

A source program is a sequence of source statements that are punched into cards. These statements may be written on the standard coding form, X28-6509 (shown in Figure 1), provided by IBM. One line of coding on the form is punched into one card. The vertical columns on the form correspond to card columns. Space is provided on the form for program identification and instructions to keypunch operators. None of this information is punched into a card.

The body of the form (Figure 1) is composed of two fields: first, the statement field, columns 1-71, and then the identification-sequence field, columns 73-80. The identification-sequence field is not part of a statement and is discussed following "Summary of Statement Format" in this section.

The entries (i.e., coding), composing a statement, occupy columns 1-71 of a line. Therefore, column 1 is referred to as the "begin" column and column 71 is referred to as the "end" column. The "begin" statement boundary may be altered by use of the Input Format Control (ICTL) assembler instruction

Figure 1. Coding Form

(discussed later) to designate an alternate begin column.

#### Statement Format

A statement can be either a comment or an instruction.

A statement may be used for a comment by placing an asterisk in the begin column. Extensive comments entries may be written by using a series of lines with an asterisk in the begin column of each line.

Instructions may consist of one to four entries in the statement field. They are, from left to right: a name entry, an operation entry, an operand entry, and a comments entry. These entries must be separated by one or more blanks, and must be written in the order stated.

Only one statement is allowed per line; a statement cannot be continued on additional lines. Column 72 must be blank. Columns 73 through 80 may contain a serial number, as discussed in Section 7, "Update Feature."

The coding form (Figure 1) is vertically ruled to provide an 8-character name field, a 5-character operation field, and a 56-character operand and/or comments field.

If desired, the programmer may disregard these column boundaries and write the name, operation, operand, and comments entries in other positions, subject to the following rules:

- The entries must not extend beyond the "begin" and "end" statement boundaries (either the conventional boundaries, or the altered boundaries).

- 2. The entries must be in proper sequence, as stated above.

- 3. The entries must be separated by one or more blanks.

- 4. If used, a name entry must start in the begin column.

A description of the name, operation, operand, and comments entries follows:

<u>Name Entries</u>: The name entry is a symbol created by the programmer to identify a statement. A name entry usually is optional. The symbol must consist of eight characters or less, and be entered with the first character appearing in the begin column. If the begin column is blank, the assembler program assumes no name has been entered. No blanks may appear in the name entry.

<u>Operation Entries:</u> The operation entry is the mnemonic operation code specifying the machine operation or assembler operation desired. An operation entry is mandatory and must start at least one position to the right of the begin column. Valid mnemonic operation codes for machine and assembler operations are contained in Appendixes D and E of this publication. Valid operation codes consist of five characters or fewer for machine or assembler-instruction operation codes. No blanks may appear within the operation entry.

Operand Entries: The operand entry is the coding that identifies and describes data to be acted upon by the instruction, by indicating such things as storage locations, masks, storage-area lengths, or types of data.

Depending on the particular instruction, an operand entry may consist of one or more operands. Operands are required for all machine instructions but not for all assembler instructions.

Operands must be separated by commas, and no blanks may intervene between operands and the commas that separate them.

The operands may not contain embedded blanks, except as follows:

If character representation is used to specify a constant, a literal, or immediate data in an operand, the character string may contain embedded blanks, e.g., C'A D'.

<u>Comments Entries:</u> Comments are descriptive items of information about the program that are to be inserted in the program listing. All 256 valid characters (see "Character Set" in this section), including blanks, may be used in writing a comment. The entry must be separated from the operand entry by a blank. The comments entry cannot extend beyond column 71.

In statements where an optional operand entry is omitted but a comments entry is desired, the absence of the operand entry must be indicated by a comma preceded and followed by one or more blanks, as follows:

| Name      | Operation | Operand   |

|-----------|-----------|-----------|

| <br> <br> | END       | , COMMENT |

Statement Example: The following example illustrates the use of name, operation, operand, and comments entries. A compare instruction has been named by the symbol COMP; the operation entry (CR) is the mnemonic operation code for a register-toregister compare operation, and the two operands (5,6) designate the two general registers whose contents are to be compared. The comments entry reminds the programmer that he is comparing "new sum" to "old" with this instruction.

| Name | Operation | Operand            |  |

|------|-----------|--------------------|--|

| COMP | CR        | 5,6 NEW SUM TO OLD |  |

## Summary of Statement Format

The entries in an instruction must always be in the following order: name, operation, operand(s), comment.

Every instruction requires an operation entry. Comments entries are optional. Name entries are required for certain instructions and are optional in all other cases. Operand entries are required for all machine instructions and most assembler instructions.

The name and operation entries must not contain embedded blanks. Operands must not have blanks preceding or following the commas that separate them.

All entries must be contained within the designated statement boundaries.

## Identification-Sequence Field

The identification-sequence field of the coding form (columns 73-80) is used to enter program identification and/or statement sequence characters. The entry is optional. If the field, or a portion of it, is used for program identification, the identification is punched in the source cards and reproduced in the program list-ing.

#### Character Set

Source statements are written using the following characters:

| <u>Letters</u> | Α | through | z, | and | \$, | <b>#</b> , | a |  |

|----------------|---|---------|----|-----|-----|------------|---|--|

|----------------|---|---------|----|-----|-----|------------|---|--|

Digits 0 through 9

Special Characters + - , = . \* ( ) ' / & blank

These characters are represented by the card-punch combinations and internal bit configurations listed in Appendix A. In addition, any of the 256 punch combinations may be designated anywhere that characters are used in comments and between paired single quotes.

#### ASSEMBLER LANGUAGE STRUCTURE

The basic structure of the language can be stated as follows.

- A source statement is composed of:

- A name entry (usually optional).

- An operation entry (required).

- An operand entry (usually required).

- Comments entry (optional).

A name entry is:

• A symbol.

An operation entry is:

• A mnemonic operation code representing a machine or assembler instruction.

An operand entry is:

• One or more operands, each composed of one or more expressions. An expression is composed of a term or an arithmetic combination of terms.

Operands of machine instructions generally represent such things as storage locations, general registers, immediate data, or constant values. Operands of assembler instructions provide the information needed by the assembler program to perform the designated operation.

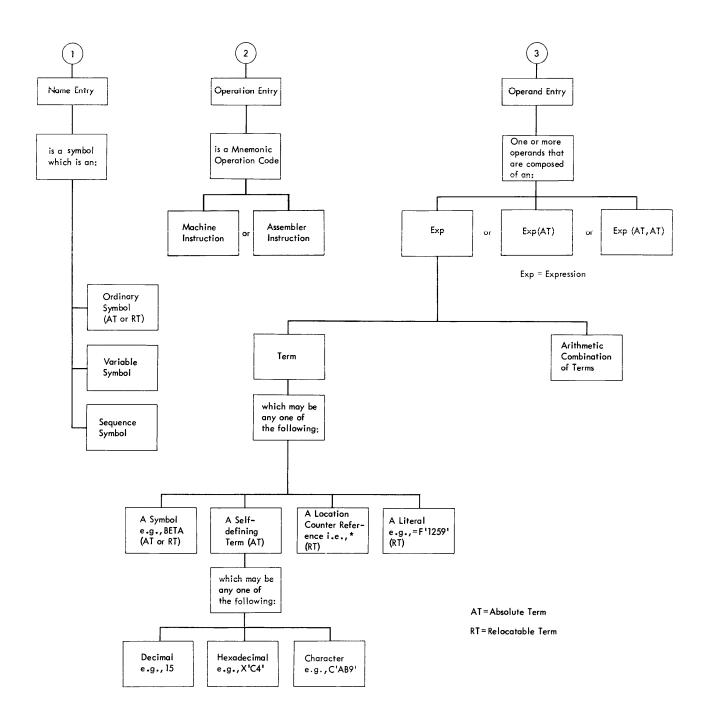

Figure 2 depicts this structure. Terms shown in Figure 2 are classed as absolute or relocatable. Terms are absolute or relocatable, depending on the effect of program relocation upon them. Program relocation is the loading of the object program into storage locations other than those originally assigned by the assembler. A term is absolute if its value does not change upon relocation. A term is relocatable if its value changes upon relocation. The following subsection "Terms and Expressions" discusses these items as outlined in Figure 2.

#### TERMS AND EXPRESSIONS

TERMS

A term is a character or combination of characters that represents a value. This value may be assigned by the assembler (symbols, location counter reference) or may be inherent in the term itself (self-defining term, literal).

An arithmetic combination of terms is reduced to a single value by the assembler.

The following material discusses each type of term and the rules for its use.

#### Symbols

A symbol is a character or combination of characters used to represent addresses or arbitrary values.

Symbols, through their use as names and in operands, provide the programmer with an efficient way to name and refer to a program element. A symbol, created by the programmer for use as a name entry and/or an operand, must conform to these rules:

- 1. The symbol must not consist of more than eight characters.

- 2. The first character must be a letter. The other characters may be letters, digits, or a combination of the two.

- 3. A symbol may not contain special characters, including blanks.

The following are valid symbols:

| READER | LOOP 2 | ab4  |

|--------|--------|------|

| A23456 | N      | \$A1 |

| X4F2   | S4     | #56  |

The following symbols are invalid, for the reasons noted:

| 256B        | (first char | acter : | is not a |

|-------------|-------------|---------|----------|

|             | letter)     |         |          |

| RECORDAREA2 |             | than    | eight    |

|             | character   | s)      |          |

| BCD*34      | (contains   | the     | special  |

|             | character   |         |          |

| IN AREA     | (contains a | blank   | )        |

DEFINING SYMBOLS: The assembler assigns a value to each symbol appearing as a name entry in a source statement. The value assigned to a symbol naming a storage area, an instruction, a constant, or a control section is the address of the leftmost byte of the storage field containing the named item. Since the address of such an item may change upon program relocation, the symbol naming it is considered a relocatable term.

A symbol used as a name entry in the Equate Symbol (EQU) assembler instruction is assigned the value designated in the operand entry of the instruction. Since the operand entry may represent a relocatable value or an absolute (i.e., nonchanging) value, the symbol is considered a relocatable term or an absolute term, depending upon the value to which it is equated.

The value of a symbol may not be negative and may not exceed 2<sup>24</sup>-1.

A symbol is said to be defined when it appears as the name of a source statement. (A special case of symbol definition involving external references is discussed in Section 3, under "Program Sectioning and Linking.")

A symbol may be defined only once in an assembly. That is, each symbol used as the name of a statement must be unique within that assembly.

<u>PREVIOUSLY DEFINED SYMBOLS</u>: Some instructions require that a symbol appearing in the operand entry be previously defined. This simply means that the symbol, before its use in an operand, must have appeared as a name entry in a prior statement.

# Self-Defining Terms

A self-defining term is one whose value is inherent in the term. It is not assigned a value by the assembler. For example, the decimal self-defining term 15 represents a value of 15.

Figure 2. Assembler Language Structure -- Machine and Assembler Instructions

There are three types of self-defining terms: decimal, hexadecimal, and character. Use of these terms is spoken of as decimal, hexadecimal, or character representation of a machine-language binary value or bit configuration.

Self-defining terms are classed as absolute terms, since the values they represent do not change upon program relocation.

<u>USING SELF-DEFINING TERMS:</u> Self-defining terms are the means of specifying machine values or bit configurations without equating the values to symbols and using the symbols.

Self-defining terms may be used to specify such program elements as immediate data, masks, registers, addresses, and address increments. The type of term selected (decimal, hexadecimal, or character) will depend on what is being specified.

The use of a self-defining term is quite distinct from the use of data constants or literals. When a self-defining term is used in a machine-instruction statement, its value is assembled into the instruction. When a data constant is referred to or a literal is specified in the operand of an instruction, its <u>address</u> is assembled into the instruction. Self-defining terms are always right-justified; truncation or padding with zeros, if necessary, occurs on the left.

Decimal Self-Defining Term: A decimal self-defining term is simply an unsigned decimal number written as a sequence of decimal digits. High-order zeros may be used (e.g., 009). Limitations on the value of the term depend on its use. For example, a decimal term that designates a general register should have a value between 0 and 15; one that represents an address should not exceed the size of storage. In any case, a decimal term may not consist of more than eight digits; to be exact, it may not exceed 16777215 (2<sup>24</sup>-1). A decimal self-defining term is assembled as its binary equivalent. Some examples of decimal self-defining terms are: 8, 147, 4092, and 00021.

<u>Hexadecimal Self-Defining Term</u>: A hexadecimal self-defining term is an unsigned hexadecimal number (written as a sequence of one to six hexadecimal digits) enclosed in single quotes and preceded by the letter X: X'C49'.

Each hexadecimal digit is assembled as its 4-bit binary equivalent. Thus, a hexadecimal term used to represent an 8-bit mask would include two hexadecimal digits. The maximum value of a hexadecimal term is FFFFFF.

The hexadecimal digits and their bit patterns are as follows:

| 0- 0000 | 4- 0100 | 8- 1000 | C- 1100 |

|---------|---------|---------|---------|

| 1- 0001 | 5- 0101 | 9- 1001 | D- 1101 |

| 2- 0010 | 6- 0110 | A- 1010 | E- 1110 |

| 3- 0011 | 7- 0111 | B- 1011 | F- 1111 |

A table for converting from hexadecimal representation to decimal representation is provided in Appendix B.

<u>Character Self-Defining Term</u>: A character self-defining term consists of one to three characters enclosed by single quotes and preceded by the letter C. All letters, decimal digits, and special characters may be used in a character term. In addition, any of the remainder of the 256 punch combinations may be designated in a character self-defining term. Examples of character self-defining terms are as follows:

| C'/'   | C' ' (blank) |

|--------|--------------|

| C'ABC' | C'13'        |

Because of the use of single quotes and ampersands as syntactic characters (ampersands are used as syntactic characters in variable symbols, which are discussed in Section 6), the following rule must be observed when using these characters in a character term:

For each single quote or ampersand desired in a character self-defining term, two single quotes or ampersands must be written. For example, the character values to the left are specified as indicated to the right:

| A¶#   | C'A''#'   |

|-------|-----------|

| B&B   | C'B&&B'   |

| • •   | C''' '''  |

| ∙ ۽ • | C'''&&''' |

Each character in the character sequence is assembled as its 8-bit code equivalent (see Appendix A). The two single quotes or ampersands that must be used to represent a single quote or ampersand within the character sequence are assembled as one single quote or ampersand.

# Location Counter Reference

The location counter reference enables the programmer to refer to the current value of the location counter. The location counter is used to assign storage addresses to program statements. It is the assembler's equivalent of the instruction counter in the computer. As each machine instruction or data area is assembled, the location counter is first adjusted to the proper boundary for the item, if adjustment is necessary, and after the statement has been processed, incremented by the length of the assembled item. Thus, after a statement has been processed, it points to the next available location. If the statement is named by a symbol, the value attribute of the symbol is the value of the location counter after boundary adjustment, but before addition of the length.

For each successively declared control section, the location counter assigns locations in consecutively higher areas of storage. The first location of each control section is aligned to a double-word boundary. (Control sections are discussed further in Section 3, "Program Sectioning and Linking.")

The location counter setting can be controlled by using the START and ORG assembler instructions, which are described in Sections 3 and 5. The maximum value for the location counter is  $2^{24}-1$ .

The programmer may refer to the current value of the location counter at any place in a program by using an asterisk as a term in an operand. The asterisk represents the location of the first byte of currently available storage (i.e., after any required boundary adjustment). Using an asterisk as the operand in a machine-instruction statement is the same as placing a symbol in the name field of the statement and then using that symbol as an operand of the statement.

A reference to the location counter may be made in an address constant literal (i.e., the asterisk may be used in an address constant specified in literal form). The address of the instruction containing the literal is used for the value of the location counter. A location counter reference may not be used in a statement that requires the use of a predefined symbol, with the exception of the EQU and ORG assembler instructions.

# <u>Literals</u>

A literal may be used to introduce data into a program. It is simply a DC operand preceded by an equal sign (=).

A literal represents data rather than a reference to data. The appearance of a literal in a statement causes the assembler program to assemble the data specified by the literal, store this data in a "literal pool," and place the address of the storage field containing the data in the operand field of the assembled statement.

Literals provide a means of entering constants (such as numbers for calculation, addresses, indexing factors, or words or phrases for printing out a message) into a program by specifying the constant in the operand of the instruction in which it is used. Specifying a literal is in contrast to using the DC assembler instruction to enter the data into the program and then specifying the name of the DC instruction in the operand. Only one literal is allowed in a machine-instruction statement.

A literal may not be combined with any other terms.

A literal may not be used as the receiving field of an instruction that modifies storage.

A literal may not be specified in an address constant (see Section 5, "DC--Define Constant").

The instruction coded below shows one use of a literal.

| Name  | Operation | Operand    |

|-------|-----------|------------|

| GAMMA | L         | 10,=F'274' |

The statement GAMMA is a load instruction using a literal as the second operand. When assembled, the second operand of the instruction will be the address at which the value F'274' is stored.

A literal may be used as an operand wherever a storage address is specified in a machine instruction or in a CCW assembler instruction operand. Literals are considered relocatable because the address of the literal, rather than the literal itself, will be assembled in the statement that employs a literal. The assembler generates the literals, collects them, and places them in a specific area of storage, as explained in the subsection "The Literal Pool." A literal is not to be confused with the immediate data in an SI instruction. Immediate data is assembled into the instruction.

Literal Format: The assembler requires a description of the type of literal being specified as well as the literal data itself. The descriptive portion of the literal must indicate the format of the constant.

The method of describing and specifying a constant as a literal is nearly identical to the method of specifying it in the operand of a DC assembler instruction. The major difference is that the literal must start with an equal sign (=), which indicates to the assembler that a literal follows. The reader is referred to the discussion of the DC assembler instruction operand format (Section 5) for the means of specifying a literal. The type of literal designated in an instruction is not checked for correspondence with the operation code of the instruction.

Some examples of literals are:

| =A(BETA)   | <br>address constant literal  |

|------------|-------------------------------|

| =F'1234'   | <br>a fixed-point number with |

|            | a length of four bytes        |

| =C ' ABC ' | <br>a character literal       |

The Literal Pool: The literals processed by the assembler are collected and placed in a special area called the literal pool, and the location of the literal, rather than the literal itself, is assembled in the statement employing a literal. The positioning of the literal pool must be assigned by the programmer within the control section in which the literal is used.

The programmer may also specify that multiple literal pools be created. However, the sequence in which literals are ordered within the pool is controlled by the assembler. Further information on positioning the literal pool(s) is in Section 5 under "LTORG--Begin Literal Pool."

## EXPRESSIONS

This subsection discusses the expressions used in coding operand entries for source statements. Two types of expressions, absolute and relocatable, are presented along with the rules for determining these attributes of an expression.

As shown in Figure 2, an expression is composed of a single term or an arithmetic combination of terms. The arithmetic operators that may be used to combine the terms of an expression are + (addition), -(subtraction), \* (multiplication), and / (division).

The following are examples of valid expressions (provided that BETA, LAMBDA, GAMMA, TEN, and TWO are absolute):

| AREA1+X'2D' B | BETA*10     |

|---------------|-------------|

| *+32 C        | ABC         |

| N-25 2        | 9           |

| FIELD L       | AMBDA+GAMMA |

| =F'1234' T    | EN/TWO      |

The rules for coding expressions are:

- An expression may not start with an arithmetic operator. Therefore, the expression -A+BETA is invalid. However, the expression 0-A+BETA is valid.

- 2. An expression may not contain two terms or two operators in succession.

- 3. An expression may not consist of more than three terms.

- 4. An expression may not have more than one level of parentheses (i.e., a parenthetical expression may not appear within a parenthetical expression).

- 5. A multiterm expression may not contain a literal.

- 6. A parenthesized expression may not contain a literal.

## Evaluation of Expressions

A single term expression, e.g., 29, BETA, \*, takes on the value of the term involved.

A multiterm expression, e.g., BETA+10, ENTRY-EXIT, 25\*10+A, is reduced to a single value, as follows:

- 1. Each term is given its value.

- 2. Every expression is computed to 32 bits.

- 3. Arithmetic operations are performed left to right. Multiplication and division are done before addition and subtraction, e.g., A+B\*C is evaluated as A+(B\*C), not (A+B)\*C. The computed result is the value of the expression.

- Division always yields an integer result; any fractional portion of the result is dropped. For example, 1/2\*10 yields a zero result, whereas 10\*1/2 yields 5.

- 5. Division by zero is valid and yields a zero result.

A parenthesized multiterm expression used in an expression is processed before the rest of the terms in the expression, e.g., in the expression BETA\*(CON-10), the term CON-10 is evaluated first and the resulting value is used in computing the final value of the expression.

Negative values are carried in two's complement form. Final values of expressions are the truncated rightmost 24 bits of the results. The value of an expression before truncation must be in the range  $-2^{24}$  through  $2^{24}-1$ . A negative result is considered to be a 3-byte positive value. Intermediate results have a range of  $-2^{31}$  through  $2^{31}-1$ .

#### Absolute and Relocatable Expressions

An expression is called absolute if its value is unaffected by program relocation.

An expression is called relocatable if its value changes upon program relocation.

The two types of expressions, absolute and relocatable, take on these characteristics from the term(s) composing them.

ABSOLUTE EXPRESSION: An absolute expression may be an absolute term or any arithmetic combination of absolute terms. An absolute term may be an absolute symbol, or any of the self-defining terms. All arithmetic operations are permitted between absolute terms.

An absolute expression may contain relocatable terms (RT) -- alone or in combination with absolute terms (AT) -- under the following conditions:

- 1. There must be an even number of relocatable terms in the expression.

- 2. The relocatable terms must be paired. Each pair of terms must have the same relocatability attribute, i.e., they appear in the same control section in this assembly (see Section 3, "Program Sectioning and Linking"). Each pair must consist of terms with opposite signs. The paired terms do not have to be contiguous, e.g., RT+AT-RT.

- No relocatable term may enter into a multiply or divide operation. Thus, RT-RT\*10 is invalid. However, (RT-RT)\*10 is valid.

The pairing of relocatable terms (with opposite signs and the same relocatability attribute) cancels the effect of relocation. Therefore, the value represented by the paired terms remains constant, regardless of program relocation. For example, in the absolute expression A-Y+X, A is an absolute term, and X and Y are relocatable terms with the same relocatability attribute. If A equals 50, Y equals 25, and X equals 10, the value of the expression would be 35. If X and Y are relocated by a factor of 100, their values would then be 125 and 110. However, the value of the expression would still be 35 (50-125+110=35). An absolute expression reduces to a single absolute value.

The following examples illustrate absolute expressions. A is an absolute term; X and Y are relocatable terms with the same relocatability attribute.

| A-Y+X          |   |

|----------------|---|

| Α              |   |

| A*A            |   |

| X-Y+A          |   |

| <b>*-</b> Y (a | 1 |

| counter        | 1 |

| relocata       | b |

\*-Y (a reference to the location counter must be paired with another relocatable term from the same control section, i.e., with the same relocatability attribute)

**<u>RELOCATABLE</u>** EXPRESSION: A relocatable expression is one whose value would change by <u>n</u> if the program in which it appears is relocated <u>n</u> bytes away from its originally assigned area of storage. All relocatable expressions must have a positive value.

A relocatable expression may be a relocatable term. A relocatable expression may contain relocatable terms -- alone or in combination with absolute terms -- under the following conditions:

- 1. There must be an odd number of relocatable terms.

- 2. All relocatable terms but one must be paired. Pairing is described in the preceding discussion of absolute expressions.

- 3. The unpaired term must not be directly preceded by a minus sign.

- 4. No relocatable term may enter into a multiply or divide operation.

A relocatable expression reduces to a single relocatable value. This value is the value of the odd relocatable term, adjusted by the values represented by the absolute terms and/or paired relocatable terms associated with it. The relocatability attribute is that of the odd relocatable term.

For example, in the expression W-X+W, the terms W and X are relocatable terms with the same relocatability attribute. If, initially, W equals 10 and X equals 15, the value of the expression is 5. However, upon relocation, this value will change. If a relocation factor of 100 is applied, the value of the expression is 105. Note that the value of the paired terms, W-X, remains constant at -5 regardless of relocation. Thus, the new value of the expression, 105, is the result of the value of the odd term (W) adjusted by the values of W-X.

The following examples illustrate relocatable expressions. A is an absolute term, W and X are relocatable terms with the same relocatability attribute, Y is a relocatable term with a different relocatability attribute.

| <b>Y-32*</b> A    | =F'1234'(literal) |

|-------------------|-------------------|

| W-X+Y             | A*A+W             |

| W-X+*             | W-X+W             |

| * (reference to   | Y                 |

| location counter) |                   |

#### ADDRESSING

The IBM System/360 addressing technique requires the use of a base register, which contains the base address, and a displacement, which is added to the contents of the base register. The programmer may specify a symbolic address and request the as-sembler to determine its storage address composed of a base register and a displacement. The programmer may rely on the assembler to perform this service for him by indicating which general registers are available for assignment and what values the assembler may assume each contains. The programmer may use as many or as few registers for this purpose as he desires. The only requirement is that, at the point of reference, a register containing an address from the same control section is available, and that this address is less than or equal to the address of the item to which the reference is being made. The difference between the two addresses may not exceed 4095 bytes.

ADDRESSES -- EXPLICIT AND IMPLIED

An address is composed of a displacement plus the contents of a base register. (In the case of RX instructions, the contents of an index register are also used to derive the address in the machine.)

The programmer writes an explicit address by specifying the displacement and the base register number. In designating explicit addresses, a base register may not be combined with a relocatable symbol.

The programmer writes an implied address by specifying an absolute or relocatable address. The assembler has the facility to select a base register and compute a displacement, thereby generating an explicit address from an implied address, provided that it has been informed as to (1) what base registers are available to it and (2) what each contains. The programmer conveys this information to the assembler through the USING and DROP assembler instructions.

# BASE REGISTER INSTRUCTIONS

The USING and DROP assembler instructions enable programmers to use expressions representing implied addresses as operands of machine-instruction statements, leaving the assignment of base registers and the calculation of displacements to the assembler.

In order to use symbols in the operand field of machine-instruction statements, the programmer must (1) indicate to the assembler, by means of USING statements, which general registers are available for use as base registers, (2) specify, by means of the USING statement, what value each base register contains, and (3) load each base register with the value he has specified for it.

A program must have at least one USING statement for each control section that contains implicit addressing.

Having the assembler determine base registers and displacements relieves the programmer of separating each address into a displacement value and a base address value. This feature of the assembler will eliminate a likely source of programming errors, thus reducing the time required to check out programs. To take advantage of this feature, the programmer uses the USING and DROP instructions described in this subsection. The principal discussion of this feature follows the description of both instructions.

#### USING -- Use Base Address Register

The USING instruction specifies a general register that is available for use as a base register. This instruction also states the base address value that the assembler may assume will be in the register at object time. Note that a USING instruction does not load the register specified. It is the programmer's responsibility to make sure that the specified base address value is placed into the register. Suggested loading methods are described in the subsection "Programming with the USING Instruction." The format of the USING instruction statement is:

| Name  | Operation | Operand                            |

|-------|-----------|------------------------------------|

| Blank |           | Two expressions<br>of the form v,r |

Operand  $\underline{v}$  must be an absolute or relocatable expression. Literals are not permitted. Operand  $\underline{v}$  specifies a value that the assembler can use as a base address. The operand  $\underline{r}$  must be an absolute term. It specifies the general register that the assembler assumes will contain the base address represented by operand  $\underline{v}$ . The value of  $\underline{r}$  must be in the range from 0 to 15.

For example, the following USING statement tells the assembler it may assume that the current value of the location counter will be in general register 12 at execution time.

| Name | Operation | Operand |

|------|-----------|---------|

|      | USING     | *,12    |

If the programmer changes the value in a base register currently being used, and wishes the assembler to compute displacement from this value, the assembler must be told the new value by means of another USING statement. In the following sequence the assembler first assumes that the value of ALPHA is in register 9. The second statement then causes the assembler to assume that ALPHA+1000 is the value in register 9.

| Name   | Operation | Operand      |

|--------|-----------|--------------|

| 1      | USING     | ALPHA,9      |

| 1      | •         |              |

| 1<br>1 | USING     | ALPHA+1000,9 |

A USING statement may specify general register 0 as a base register if operand v is a relocatable expression from any control section in the program or has an absolute value of zero. If general register 0 is specified, the assembler assumes that register 0 contains the value zero. Note: If register 0 is made available by a USING instruction, the program is not relocatable, despite the fact that the value specified by operand v must be relocatable. However, the programmer is able to make the program relocatable at some future time by:

- 1. Replacing register 0 with an alternate register in the USING statement.

- Inserting an instruction that loads the alternate register with a relocatable value.

- 3. Reassembling the program.

# DROP -- Drop Base Register

The DROP instruction specifies a previously available register that may no longer be used as a base register. The format of the DROP instruction statement is as follows:

| Name  | Operation | Operand           |

|-------|-----------|-------------------|

| Blank | DROP      | One absolute term |

The absolute term indicates a general register previously named in a USING statement that is now unavailable for base addressing. The following statement, for example, prevents the assembler from using register 7:

| Name | Operation | Operand |

|------|-----------|---------|

|      | DROP      | 7       |

It is not necessary to use a DROP statement when the base address being used is changed by a USING statement; nor are DROP statements needed at the end of the source program.

A register made unavailable by a DROP instruction can be made available again by a subsequent USING instruction.

# PROGRAMMING WITH THE USING INSTRUCTION

The USING (and DROP) instructions may be used anywhere in a program, as often as needed, to indicate the general registers that are available for use as base registers and the base address values that the assembler may assume each contains at execution time. Whenever an address is specified in a machine-instruction statement, the assembler determines whether there is an available register containing a suitable base address. A register is considered available for a relocatable address if it was specified in a USING instruction to have a relocatable value. A register with an absolute value is available only for absolute addresses. In either case, the base address is considered suitable only if it is less than or equal to the address of the item to which the reference is made. The difference between the two addresses may not exceed 4095 bytes. In calculating the base register to be used, the assembler will always use the available register giving the smallest displacement. If there are two registers with the same value, the highest numbered register will be used.

| Name   | Operation | Operand       |

|--------|-----------|---------------|

| BEGIN  | BALR      | 2,0           |

|        | USING     | HERE, 2       |

|        | USING     | HERE+4096,3   |

|        | USING     | HERE+8192,4   |

|        | USING     | HERE+12288,5  |

| HERE   | L         | 3, BASEAD     |

|        | L         | 4,BASEAD+4    |

|        | L         | 5,BASEAD+8    |

|        | B         | FIRST         |

| BASEAD | DC        | A(HERE+4096)  |

|        | DC        | A(HERE+8192)  |

|        | DC        | A(HERE+12288) |

| FIRST  | •         |               |

|        | 1.        | 1             |

|        | 1.        | 1             |

| LAST   | 1.        |               |

|        | END       | BEGIN         |

| Name           | Operation     | Operand |

|----------------|---------------|---------|

| BEGIN          | BALR<br>USING | 2,0     |

| FIRST          | •             |         |

| <br>  LAST<br> | END           | BEGIN   |

In the preceding sequence, the BALR instruction loads register 2 with the address of the immediately following storage location. In this case, it is the address of the instruction named FIRST. The USING instruction indicates to the assembler that register 2 contains this location. When employing this method, the USING instruction must immediately follow the BALR instruction. No other USING or load instructions are required if the location named LAST is within 4095 bytes of FIRST.

In the following sequence, the BALR and L instructions load registers 2 through 5. The USING instructions indicate to the assembler that these registers are available as base registers for addressing a maximum of 16,384 consecutive bytes of storage, beginning with the location named HERE. The number of addressable bytes may be increased or decreased by changing the number of registers designated by the USING and L instructions and the number of address constants specified in the DC instruction.

## RELATIVE ADDRESSING

Relative addressing is the technique of addressing instructions and data areas by designating their location in relation to the location counter or to some symbolic location. This type of addressing is always in bytes, never in bits, words, or instructions. Thus, the expression \*+4 specifies an address that is four bytes greater than the current value of the location counter. In the sequence of instructions shown in the following example, the location of the CR machine instruction can be expressed in two ways, ALPHA+2 or BETA-4, because all of the mnemonics in the RR format.

| Name  | Operation | Operand            |

|-------|-----------|--------------------|

| ALPHA | CR<br>BCR | 3,4<br>4,6<br>1,14 |

| BETA  | AR        | 2,3                |

#### PROGRAM SECTIONING AND LINKING

It is often convenient, or necessary, to write a program in sections. The sections may be assembled separately, then combined via the linkage editor into one or more executable phases. The assembler provides facilities for creating multisectioned programs and symbolically linking separately assembled programs or program sections. The combined number of control sections and dummy sections plus the number of unique symbols in EXTRN statements may not exceed 255.

Sectioning a program is optional, and many programs can best be written without sectioning. The programmer writing an unsectioned program need not concern himself with the subsequent discussion of program sections, which are called control sections. He need not employ the CSECT instruction, which is used to identify the control sections of a multisection program. Similarly, he need not concern himself with the discussion of symbolic linkages if his program neither requires a linkage to nor receives a linkage from another program. He may, however, wish to identify the program and/or specify a tentative starting location for it, both of which may be done by using the START instruction. He may also want to employ the dummy section feature obtained by using the DSECT instruction.

<u>Note:</u> Program sectioning and linking is closely related to the specification of base registers for each control section. Sectioning and linking examples are provided under the heading "Addressing External Control Sections."

#### CONTROL SECTIONS

The concept of program sectioning should be taken into consideration at coding time, assembly time, and load time. To the programmer, a program is a logical unit. He may want to divide it into sections called control sections; if so, he writes it in such a way that control passes properly from one section to another regardless of the relative physical position of the sections in storage. A control section is a block of coding that can be relocated independently (i.e., without affecting the location of other coding), at load time, without altering or impairing the operating logic of the program. It is normally identified by the CSECT instruction. However, if it is desired to specify a tentative starting location, the START instruction may be used to identify the first control section.

To the assembler, there is no such thing as a program; instead, there is an assembly, which consists of one or more control sections. (However, the terms assembly and program are often used interchangeably.) An unsectioned program is treated as a single control section. To the linkage editor, there are no programs, only control sections that must be fashioned into an object program.

The assembler output consists of the assembled control sections and a control dictionary. The control dictionary contains information the linkage editor needs to complete cross-referencing between control sections as they are combined into an object program. The linkage editor can object program. The linkage editor can combine control sections from various assemblies with the help of the corresponding control dictionaries. Successful combination of separately assembled control sections depends on the techniques used to provide symbolic linkages between the control sections. Whether the programmer writes an unsectioned program, a multisectioned program, or part of a multisectioned program, he still knows what eventually will be entered into storage because he has described storage symbolically. He may not know where each section appears in storage, but he does know what storage contains. There is no constant relationship between control sections. Thus, knowing the location of one control section does not make another control section addressable bv relative addressing techniques.

#### Control Section Location Assignment

Locations are assigned to control sections as if the sections are placed in storage consecutively, in the same order as they first occur in the program. Each control section subsequent to the first begins at the next available double-word boundary.

#### START -- Start Assembly

The START instruction may be used to give a name to the first (or only) control section of a program. It may also be used to specify an initial location counter value for the program. The format of the START instruction statement is as follows:

| Name                 | Operation | Operand                           |

|----------------------|-----------|-----------------------------------|

| A symbol<br>or blank | •         | A self-defining<br>term, or blank |

If a symbol names the START instruction, the symbol is established as the name of the control section. Otherwise, the control section is considered to be unnamed. All subsequent statements are assembled as part of that control section. This continues until an instruction identifying a different control section (CSECT, DSECT, or COM) is encountered.

The symbol in the name field is a valid relocatable symbol whose value represents the address of the first byte of the control section.

The assembler uses the self-defining term specified by the operand as the initial location counter value of the program. This value should be divisible by eight. For example, either of the following statements could be used to assign the name PROG2 to the first control section and to indicate an initial assembly location of 2040.

| Name | Operation | Operand        |

|------|-----------|----------------|

| 1    |           | 2040<br>X'7F8' |

If the operand is omitted, the assembler sets the initial location counter value of the program at zero. The location counter is set at the next double-word boundary when the value of the START operand is not divisible by eight.

Note: The START instruction may not be preceded by any type of assembler language statement that may either affect or depend upon the setting of the location counter.

# <u>CSECT -- Identify Control Section</u>

The CSECT instruction identifies the beginning of a control section. The format of the CSECT instruction statement is as follows:

| Name                 | Operation | Operand       |

|----------------------|-----------|---------------|

| A symbol<br>or blank | CSECT     | Must be blank |

If a symbol names the CSECT instruction, the symbol is established as the name of the control section; otherwise, the section is considered to be unnamed. Multiple CSECT instructions must have unique names. The name of a CSECT may be blank, provided that no other CSECT or START instruction has a blank name.

The symbol in the name field is a valid relocatable symbol whose value represents the address of the first byte of the control section.

The occurrence of a CSECT instruction terminates the previous control section.

#### Unnamed Control Section

If it is desired to write a program that is unsectioned, the program does not need to contain a CSECT or START instruction. In this case, the assembler will generate an unnamed START statement for the first assembler language statement that may either affect or depend upon the setting of the location counter.

#### DSECT -- Identify Dummy Section

A dummy section represents a control section that is assembled but is not part of the object program. A dummy section is a convenient means of describing the layout of an area of storage without actually reserving the storage. (It is assumed that the storage is reserved either by some other part of this assembly or else by another assembly.) The DSECT instruction identifies the beginning of a dummy section. More than one dummy section may be defined per assembly, but each must be named. The format of the DSECT instruction statement is as follows:

| Name     | Operation | Operand       |

|----------|-----------|---------------|

| A symbol | DSECT     | Must be blank |

The symbol in the name field is a valid relocatable symbol whose value represents the first byte of the section.

All statements following the DSECT instruction are assembled as part of that control section until a statement identifying a different control section is encountered (i.e., another DSECT, CSECT, or COM instruction). All assembler language instructions may occur within dummy sections. Symbols that name statements in a dummy section may be used in USING instructions. Therefore, they may be used in program elements (e.g., machine-instructions and data definitions) that specify storage addresses. An example illustrating the use of a dummy section appears subsequently under "Addressing Dummy Sections."

The occurrence of a DSECT instruction terminates the previous control section. A DSECT cannot be resumed.

Note: A symbol that names a statement in a dummy section may be used in an A-type address constant only if it is paired with another symbol (with the opposite sign) from the same dummy section.

<u>DUMMY SECTION LOCATION ASSIGNMENT</u>: A location counter is used to determine the relative locations of named program elements in a dummy section. The location counter is always set to zero at the beginning of the dummy section, and the location values assigned to symbols that name statements in the dummy section are relative to the initial statement in the section.

ADDRESSING DUMMY SECTIONS: The programmer may wish to describe the format of an area whose storage location will not be determined until the program is executed. He can describe the format of the area in a dummy section, and he can use symbols defined in the dummy section as the operands of machine instructions. To effect references to the storage area, he does the following:

1. Provides a USING statement specifying both a general register that the assembler can assign to the machineinstructions as a base register and a value from the dummy section that the assembler may assume the register contains. 2. Ensures that the same register is loaded with the actual address of the storage area.

The values assigned to symbols defined in a dummy section are relative to the initial statement of the section. Thus, all machine instructions which refer to names defined in the dummy section will, at execution time, refer to storage locations relative to the address loaded into the register.

| Operation                                                                     | Operand                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSECT<br>BALR<br>USING                                                        | 2,0<br>*,2                                                                                                                                                                                                                              |

| USING<br>CLI<br>BE                                                            | INAREA,3<br>INCODE,C'A'<br>ATYPE                                                                                                                                                                                                        |

| LA<br>LA<br>LA<br>ST<br>LA<br>BCT<br>LA<br>LA<br>LA<br>LH<br>STH<br>LA<br>BCT | <pre>5,0 6,5 7,INPUTA(5) 7,WORKA(5) 5,4(5) 6,*-12 5,0 6,9 7,INPUTB(5) 7,WORKB(5) 5,2(5) 6,*-12</pre>                                                                                                                                    |

|                                                                               | 5F<br>9H                                                                                                                                                                                                                                |

| DSECT<br>DS<br>DS<br>DS<br>DS                                                 | CL1<br> 5F<br> 9H                                                                                                                                                                                                                       |

|                                                                               | CSECT<br>BALR<br>USING<br>CLI<br>BE<br>CLI<br>BE<br>CLI<br>BE<br>CLI<br>BE<br>CLI<br>CLI<br>BE<br>CLI<br>CLI<br>BE<br>CLI<br>CLI<br>BE<br>CLI<br>CLI<br>CLI<br>BE<br>CLI<br>CLI<br>CLI<br>CLI<br>CLI<br>CLI<br>CLI<br>CLI<br>CLI<br>CLI |